The 65nm architecture used to fabricate the chip allows for large scale production at low costs.

Updated: Jun 17, 2024 07:50 AM EST

Stock photo of 3D illustration of a glowing CPU installed on a generic mainboard.

Researchers at the Tokyo Institute of Technology, in collaboration with the National Institute of Information and Communications Technology (NICT) in Japan, have built a novel wireless chipset with a data transmission rate of 640 Gbps.

The chip can be fabricated using the Complementary Metal-Oxide-Semiconductor (CMOS) process, making it cost-effective and suitable for large-scale production.

We currently use millimeter-wave frequency bands to meet the increasing demand for faster wireless internet services that can also process large amounts of data.

The fifth generation of mobile internet services, popularly known as 5G, operates at a frequency of 24-47 GHz and can offer data transfer speeds as high as 10 Gbps.

The next generation of this communication network will use bands in the frequency range of 110-170 GHz, and wireless chipsets that can operate in this range need to be developed. However, at these frequencies, there is an increased likelihood of attenuation – loss in the amplitude of the signal.

So, the chipset must be designed to ensure that the generated signal can maintain its strength.

The 640 Gbps chipset

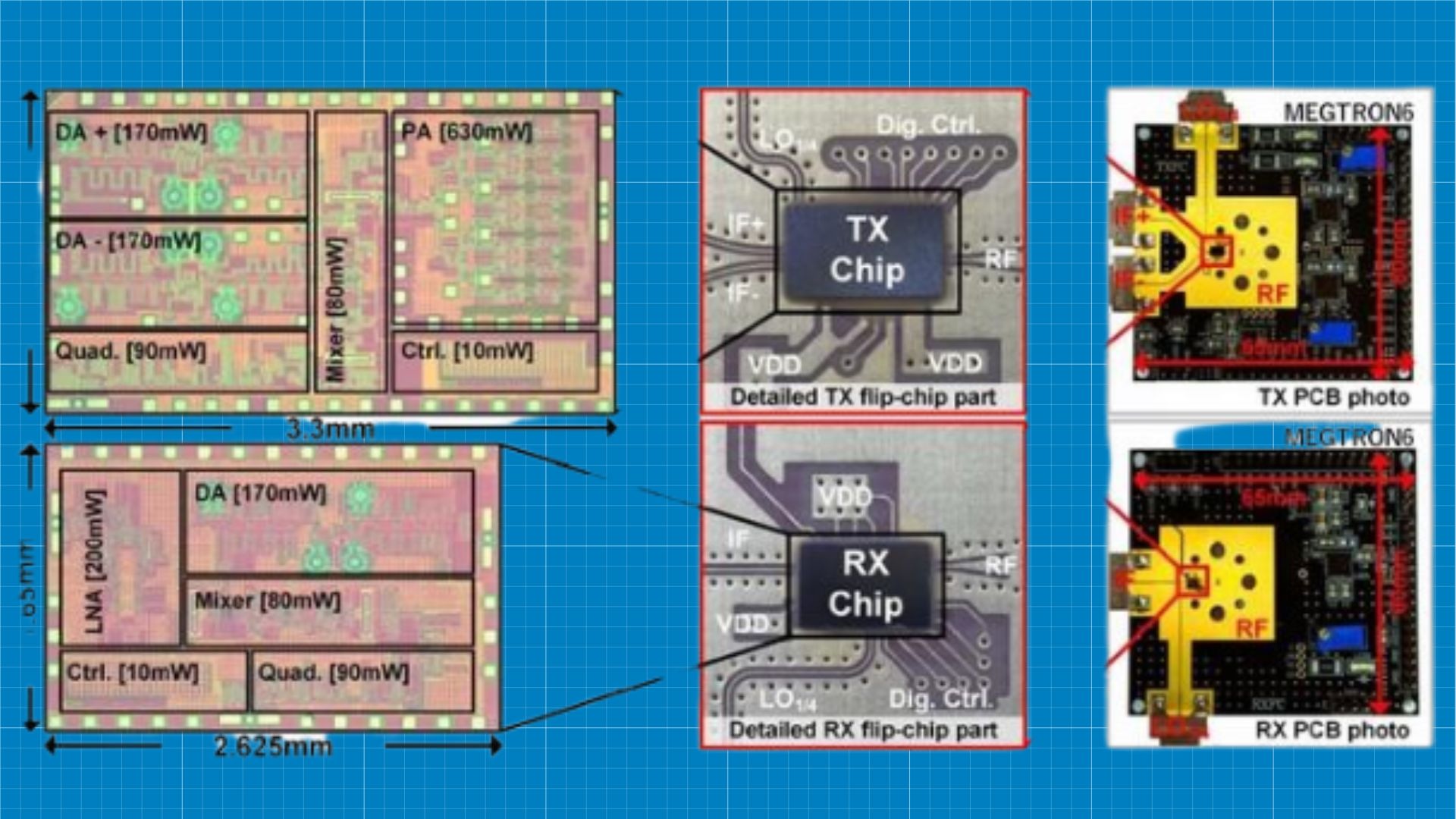

The researchers, led by Kenichi Okada, a professor at the School of Engineering at the Tokyo Institute of Technology, used the 65 nm silicon architecture to make a chipset with a bandwidth of 56 GHz.

The transceiver chip consists of both transmitting and receiving integrated circuits (IC). The transmitting component measures only 1.87 mm x 3.30 mm, while the receiving component measures 1.65 mm x 2.60 mm.

The chip is also equipped with a wide range of amplifiers to improve the signal quality. For instance, low-noise amplifiers boost signal strength while minimizing noise, while distributed amplifiers improve the signal’s linearity. A frequency converter embedded in the chip allows the frequency to be adjusted to the desired range.

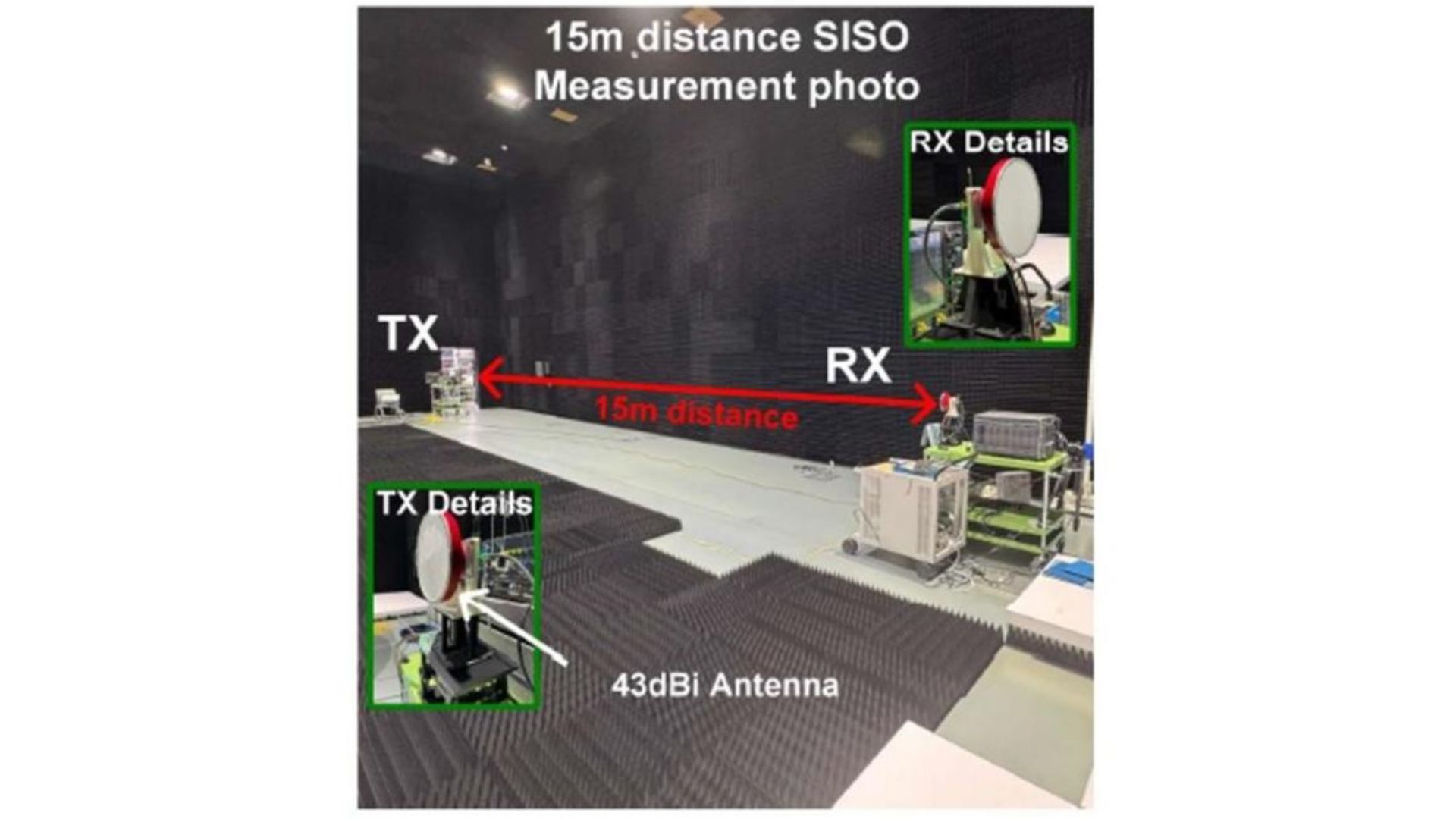

To assess the chip’s capabilities, the researchers paired it with an external antenna, using the waveguide format instead of the transmission line format for signal transmission.

How did the chip perform?

Using this chipset, the researchers successfully demonstrated high linearity for multi-level modulation. With a modulated signal with 32 QAM (Quadrature Amplitude Modulation) and a symbol rate of 40 Gbaud, the researchers achieved a transmission speed of 200 Gbps. The bit error rate was less than 10-3.

When using 16 QAM modulation, the researchers successfully achieved speeds of 120 Gbps over a distance of nearly 50 feet (15 m).

RECOMMENDED ARTICLES

To test the chip in a multiple-input and multiple-output configuration, the researchers connected it to four transmitter and four receiver modules, where each antenna could handle its own data stream.

In 16 QAM modulation, each antenna reached speeds of 160 Gbps, delivering a total transmission speed of 640 Gbps. This is up to 100 times faster than 5G systems currently available in the market.

“The proposed chipset holds promise for the next generation of wireless systems to support automated cars, telemedicine, and advanced virtual reality experiences,” Okada said in a press release.

The research findings were presented at the 2024 IEEE Symposium on VLSI Technology & Circuits, which is being held this week in Honolulu, USA.

The Blueprint Daily

Stay up-to-date on engineering, tech, space, and science news with The Blueprint.

ABOUT THE EDITOR

Ameya Paleja Ameya is a science writer based in Hyderabad, India. A Molecular Biologist at heart, he traded the micropipette to write about science during the pandemic and does not want to go back. He likes to write about genetics, microbes, technology, and public policy.

POPULAR ARTICLES

RELATED ARTICLES

This post was originally published on the 3rd party mentioned in the title ofthis site